# NAND Flash Memory 기반 저장장치 기술 동향

#### 방관후·박상훈·정의영 (연세대학교)

### l. 서 론

정보화 시대의 도래와 수많은 멀티미디어 기반의 서비스들로 말미암아 년간 새롭게 창조, 접근, 복제되는 정보의 양이 2002년의 5 Exa Byte (EB)에서 2007년에는 281 EB로 증가하였으며, 현재도 5년에 10배 정도의 속도로 정보량이 늘어나고 있다.[1] 1 EB는 DVD급의 영상을 50,000년의 시간 동안 저장할 경우에 상응하는데이터 크기로, 현재 처리되고 있는데이터양이얼마나 방대한지를 쉽게 짐작할 수 있다.이러한정보량 증가 추세에 따라,데이터를 효과적으로저장하는 매체에 대한 연구와 발전이 끊임없이진행되고 있다. 최근 IT 산업에서 이러한 목적에비추어 가장 큰 주목을 받고 있는 저장 매체 중하나가 바로 NAND flash memory이다.

NAND flash memory는 또 다른 flash memory의 한 종류인 NOR flash memory 대비 집적도가 높다는 장점이 있다. 고집적도에 따른 낮은 가격의 NAND flash memory는 최근의 정보 사회의 수요를 감당하기에 적합한 매체로 인식되어 폭발적으로 성장해왔다. 현재 디지털 카메라나 USB 메모리와 같은 대용량의 데이터 저

장이 필요한 여러 응용 분야에서 NAND flash memory가 폭넓게 사용되면서 전체 메모리 시장을 주도하고 있다.<sup>[2]</sup>

특히 지금까지 서버나 개인용 컴퓨터의 성능 향상의 발목을 잡던 hard disk drive (HDD)를 대체하기 위해 등장한 고성능 대용량 저장장치인 solid-state disk (SSD)의 핵심 저장 매체로 NAND flash memory가 사용되고 있다. 기계적인 부분이 필수불가결한 HDD에 비해 모든 구성부품이 반도체로 이루어져 있는 SSD는 성능, 전력소모, 소음, 내구성, 폼팩터 (form factor) 측면에서 모두 우수하다는 평가를 받고 있다. 한해약 340억 달러 시장 규모의 저장장치 분야에서, SSD는 고성능을 요구하는 서버나 하이엔드 급개인용 컴퓨터를 수요로 하여 큰 비중을 차지하고 있다. [3]

본고에서는 NAND flash memory에 대한 기 본적인 이해를 바탕으로 NAND flash memory 기반의 저장장치들을 소개하고, 그 중 가장 활발 하게 연구되고 있는 저장장치인 SSD 및 관련 기술들을 소개한다. Ⅱ장에서는 NAND flash memory에 대한 기본적인 내용을 소개하고, Ⅲ 장에서는 다양한 NAND flash memory 기반 저 장장치를 소개한다. IV장에서는 특히 SSD 중심의 기술 동향을 소개하고 나서 마지막으로 V장에서 전체에 대한 결론으로 마무리한다.

### II. NAND Flash Memory

Flash memory란 전기적으로 데이터를 지우고 다시 기록할 수 있는 비휘발성 (non-volatile) 메모리의 한 종류로서 플로팅 게이트 트랜지스터로 구성된 큰 배열 각각에 하나의 비트 정보를 저장한다. 이는 1984년 도시바에서 근무하고 있던 마쓰오카 후지오 박사에 의해 처음 개발되어 IEEE 1984 International Electron Devices Meeting에서 발표되었으며, 메모리 전체의 내용이 지워지는 과정을 카메라의 flash에 빗대어 flash memory라고 명명되었다.

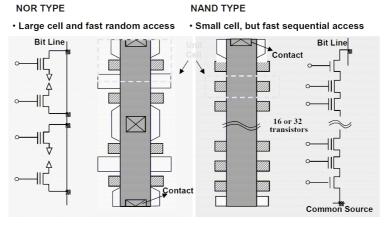

초기에는 임의 읽기 및 쓰기 (random read and write) 성능이 뛰어난 NOR flash memory 가 주류를 이루었지만, 집적도에 따른 가격의 이 슈로 NAND flash memory로 대치되고 있다. <그림 1>에 보인 바와 같이, NAND flash

memory는 NOR flash memory 대비 셀 당 contact의 개수가 훨씬 적어 높은 집적도를 가짐으로써 bit당 가격이 낮고 프로그램과 지우기 연산의 속도가 빠르다는 장점이 있다.

NAND flash memory의 가장 큰 한계는 프로그램 및 읽기 연산은 수 KB 수준의 하나의 페이지 단위로 이루어지지만 지우기 연산은 이를 대량으로 합친 블록 단위로 이루어짐으로써 연산의 기본 단위가 매우 큼과 동시에 기본적으로 덮어쓰기가 불가능한 구조이므로 한 블록의 전체를 지우기 전까지는 프로그램 연산 단위의 데이터 갱신이 불가능하다는 것이다. 더불어 기존 HDD와 비교할 때 가장 큰 단점이라고 꼽히는 것중 한 가지는 프로그램-지우기 연산 사이클로나타내어지는 수명의 제약이 있다는 것이다.

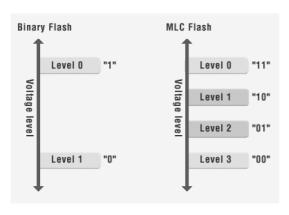

앞에서 언급한 것처럼 NAND flash memory 는 NOR flash memory보다 높은 집적도를 보이 면서 현재 상용화된 비휘발성 메모리 중에 가장 집적도가 높은 메모리임에도 더욱 높은 집적도 를 확보하기 위한 연구 개발이 진행되고 있다. 이 연구의 결과로 기존에는 메모리 셀 하나당 한 개 의 bit를 저장하던 Single-Level Cell (SLC)

〈그림 1〉NAND flash memory 와 NOR flash memory의 cell array 구조[4]

을 뛰어넘어 다수의 bit을 하나의 셀에 저장할 수 있는 Multi-Level Cell (MLC) NAND flash memory가 탄생되었다.

MLC NAND flash memory는 <그림 2>에서 와 같이 기존의 0과 1의 2개의 전압 단계로만한 셀의 상태를 구분하던 것에서 다수의 전압 단계로 구분하여 한 셀에 2-bit 이상의 데이터를 저장할 수 있게 된다. 물론 이러한 기술은 같은 부피의 제품에 더욱 많은 데이터를 저장할 수 있는 장점이 있지만, 더욱 많은 단계의 전압 레벨을 정밀하게 저장하고 판별해야 하므로 전체적인 접근 속도가 SLC NAND flash memory와비교하면 더 느려질 수밖에 없다. 더불어 세밀한단계구분 때문에 Bit Error Rate (BER) 또한높아질 수밖에 없으므로 SLC NAND flash memory 대비 오류 정정을 위해 더 복잡한 지원이 필요해지며, IV 장에서 보다 상세히 설명하도록 한다.

마지막으로, NAND flash memory가 다른 flash memory 대비 높은 집적도와 낮은 가격으로 시장을 주도함에 따라 이의 표준화 작업 또한 활발하게 이루어지고 있다. NAND flash memory의 interface에 대한 표준화 노력으로는 Hynix,

〈그림 2〉SLC (Binary) 및 2-bit MLC flash memory의 bit 저장 구조<sup>[5]</sup>

Intel 등을 주축으로 한 Open NAND Flash Interface (ONFI) [6] 와, Samsung, Denali 등을 주축으로 한 Toggle-mode DDR NAND Flash technology가 존재한다. 아직 어느 쪽이 우세하다고 말하기는 어려운 형국이지만, 공정의 발전에 따라 기존 자기 디스크 대비 단점을 뛰어넘고 안정도와 집적도를 꾸준히 높여가며 NAND flash memory가 시장에서의 우위를 확고히 다지고 있는 것만은 확실하다.

## III. NAND Flash Memory 기반 저장장치

NAND flash memory의 설계 및 공정 기술의 발전에 따라, 안정성, 성능 및 가격에 대한 개선 이 지속적으로 이루어지고 있으며, 이를 바탕으 로 한 대량 생산을 통하여 다양한 응용분야에 적 용되고 있다.

이 중 우리 주변에서 가장 쉽게 찾아볼 수 있는 응용 분야로는 휴대용 기기에서 사용되는 대용량 저장 메모리를 들 수 있다. Compact Flash (CF)나 Secure Digital (SD) 등 다양한 방식의 대용량 저장장치들은 NAND flash memory의용량, 가격, 속도상의 이점이 없이는 크게 발전하기 어려웠을 것이다. 예를 들어 CF 메모리는 그폼팩터가 크고 이른 시기에 개발되었기 때문에 NOR flash memory를 사용하기도 하였지만, 보다 높은 집적도를 가지는 NAND flash memory로 전환하게 된다. CF 메모리 이후의 휴대용 기기용 대용량 저장장치들은 작은 폼팩터와 큰 용량을 유지하기 위하여 NAND flash memory를 주로 사용하게 된다. 휴대용 기기용 대용량 저장 장치들은 불휘발성이면서 집적도가 높은 NAND

flash memory 특성을 효과적으로 활용한 것이라 할 수 있겠다.

공정의 발달과 함께 NAND flash memory의 집적도가 지속적으로 상승함에 따라 휴대용 기기를 위한 저장장치뿐만 아니라 메모리 자체를 휴대하면서 간편한 데이터 이동에 사용하기 위한 저장장치가 개발되기 시작했다. USB 방식의 휴대용 메모리가 바로 그것이다. 이는 대용량의 NAND flash memory와 이에 접근하고 USB 방식으로 전송할 수 있는 제어기 (controller)로 이루어져 있는 간단한 구조이다. USB 메모리는 기존의 플로피 디스크나 CD가 가지고 있던 이동가능한 디스크를 대체하면서 빠르게 성장하여 최근에는 플로피 디스크는 이제는 사용되지 않는 수준에 이르게 되었다.

비록 NAND flash memory가 기존의 휘발성 memory에 비하면 속도가 느리긴 하지만 위와 같은 휴대용 저장장치로만 사용이 국한되지 않는다. 서론에서도 언급한 것처럼 NAND flash memory는 SSD라고 불리는 고성능 저장장치의 내부 저장매체로 사용되고 있다. 기존의 HDD가 기계적인 부분의 한계로 성능상의 단점을 보이지만, SSD는 상대적으로 월등히 빠른 반응속도의 반도체로만 제작된 대용량 저장장치로 주목 받고 있으며 이에 관한 연구가 활발히 진행되고 있다. [7,8] 이는 불휘발성이면서 빠른 연속 접근과 빠른 읽기 속도라는 NAND flash memory의 특성을 잘 활용한 예라고 할 수 있을 것이다.

이처럼 NAND flash memory는 주로 불휘발 성이며 고집적도의 memory를 요구하는 응용분 야에서 사용되고 있다. 본고에서는 그 중 향후 기 술 개발이 가장 활발하게 일어날 것으로 예측되 는 SSD에 대하여 다음 장에서 더욱 자세히 다루 도록 하려고 한다.

### IV. Solid-State Disk 기술 동향

#### 1. Interface

SSD는 기존의 HDD를 대체하면서 더욱 고성 능으로 동작하는 것을 목표로 개발되고 있다. 따라서 추가적인 지원 없이도 기존의 컴퓨터에 연결하여 사용할 수 있는 interface를 사용하는 것이 필수적이다. 따라서 최초의 SSD는 기존의 HDD를 그대로 따라서 Advanced Technology Attachment (ATA) 방식으로 개발되었다. 과거의 Parallel ATA (PATA)에서부터 등장했던 SSD는 현재 Serial ATA (SATA) 방식으로 변경되어 HDD와 동일한 interface로 시장에서 널리 보급되고 있다. SATA는 초당 최대 150MB의 전송 속도를 지원하는 1.0에 이어 초당 300MB를 지원하는 2.0이 개발되었고, 최근에는 초당 750MB를 지원하는 3.0이 등장하여고 성능의 차세대 디스크를 지원하고 있다.

이와 달리 기존의 HDD와 interface에서부터 차별을 보여주는 SSD들도 등장하였다. 기존의 컴퓨터 내부의 각각의 장치들의 연결 표준인 Peripheral Component Interconnect (PCI)는 버스 형태를 고려하여 개발되었다. 하지만, 이는 고속의 데이터 전송에 적합하지 않았기 때문에 이를 극복하기 위해 PCI express 프로토콜이 등장하게 되었다. PCI express는 하나의 lane 당 250MB/s의 전송 속도를 가진 고속의 serial interface를 여러 lane으로 묶을 수 있도록 설계되어 PCI 방식보다 훨씬 더 높은 대역폭을 가능하게 해주었다. 최근에는 이를 SSD의 interface로 사용하여 데이터 전송 속도를 극대화한 SSD가 출시되고 있다. PCI express 역시 현재 3.0까지 등장하면서 고속 interface의 성능이 향상

하고 있다. 이외에도 DDR SDRAM interface를 이용하여 64bit 버스를 통해 초당 수십 GB를 전 송할 수 있는 SSD interface가 연구되고 있는 만큼, 당분간 SSD의 interface로 인한 병목 현 상은 나타나지 않을 것이라 예상된다.

#### 2. Cache Buffer

SSD가 NAND flash memory를 주요 memory 로 사용하기 때문에 겪는 가장 큰 문제점 중 하 나는 임의 접근 속도의 저하이다. 이는 데이터의 갱신이 지우기 연산의 선행 없이는 불가능한 NAND flash memory 특성에서 기인한다. 이러 한 문제점의 해결을 위해 많은 SSD들이 내부에 더욱 빠른 memory인 DRAM 등을 이용하여 cache buffer를 채용한다. 더불어 이러한 cache buffer를 보다 효율적으로 이용하기 위한 활발한 연구가 진행되고 있다. [9,10] 이러한 알고리즘들은 기존 중앙연산장치 등의 cache에 사용되는 정책 인 direct-mapped, set-way associative와 같 은 고전적인 방법 대신, NAND flash memory의 특성을 고려한 cache buffer 관리 알고리즘을 통해 garbage collection에 대한 부담을 줄이는 것을 목적으로 하고 있다.

하지만, 이러한 알고리즘들의 가장 큰 약점이라면 역시 휘발성 메모리를 cache buffer로 사용한다는 것이다. 휘발성 메모리는 전원 공급이차단되면 저장하고 있던 내용이 소실되므로 write—through 방식이 아닌 write—back 방식의 cache buffer를 사용하면 데이터 안정성에문제가 생길 수 있다. 이런 상황은 작은 크기와소음, 그리고 저전력으로 말미암아 휴대용 장치의 대용량 저장장치로 주목받고 있는 SSD들에게 치명적인 약점으로 작용할 수 있다. 따라서 대

부분의 cache buffer 관리 알고리즘들은 보조 전원을 가정하고 있다. 보조 전원은 시스템 전원이 어떠한 이유로든 갑자기 차단되면 보조의 전원을 이용하여 휘발성 메모리의 내용을 비휘발성 메모리인 NAND flash memory로 옮겨 데이터를 보존할 수 있도록 하여 휘발성 메모리를 데이터 손실 걱정 없이 사용할 수 있도록 해준다. 이미 이러한 개념은 휘발성 메모리를 대용량 저장장치로 사용하기 위해서 도입된 바 있으며 고성능 SSD에서는 이미 일부 적용되고 있는 기술이다. 따라서 NAND flash memory 자체의 한계를 뛰어넘기 위하여 앞으로는 이러한 보조 전원에 관한 기술발전으로 휘발성 메모리를 보다빠른 cache buffer로 활용하는 연구가 활발히진행될 것으로 보인다.

또한, 차세대 메모리라고 불리는 PRAM과 같이 비휘발성이면서도 NAND flash memory의 단점을 보완할 수 있는 메모리들을 cache 등으로 활용하는 연구 또한 이미 활발하게 진행되고 있다. [11] 앞으로 이와 같은 차세대 메모리들이 본격적으로 양산된다면 더욱 적극적인 연구가 진행되리라 판단된다.

### Error Correcting Code for NAND Flash Memory

Error Correcting Code (ECC)는 무선 통신 및 다양한 분야에서 전송 데이터의 에러를 감지하고 정정하기 위하여 사용되고 있는 기법이다. NAND flash memory 또한 여러 가지 원인으로 저장된 데이터에 error가 발생할 수 있기 때문에이러한 error를 보정하고자 ECC 기법을 사용하게 된다.

NAND flash memory 기반 저장장치 및

HDD에서 일반적으로 사용 가능한 수준으로 인정되는 Bit Error Rate (BER)는 ECC 적용 후  $10^{-13}$ 에서  $10^{-16}$ 정도이다. 이 정도 수준의 BER을 보장하기 위한 NAND flash memory에 대한 ECC는 두 가지 정도의 문제점이 있다.

첫 번째로, 적절한 채널 모델이 정의되지 않아서 적절한 알고리즘의 개발이 힘들다. 예를 들어무선 통신의 경우 Additive White Gaussian Noise (AWGN)을 가정하고 여러 알고리즘을 고안할 수 있으나 NAND flash memory의 경우적절한 채널 모델이 정의되지 않아 알고리즘 고안에 어려움이 있다. 다만 에러를 발생시키는 원인으로 write, retention, read disturb와 같은 원인들이 존재하고 그에 따른 error를 분석하는 연구가 활발히 진행되고 있다.

두 번째로는, MLC와 같이 높은 error rate를 보이는 NAND flash memory가 사용되고 있으나 그에 비해 높은 전송속도의 유지라는 제한 조건 때문에 알고리즘의 선택이 제한적이다. ECC 기법으로는 Hamming, BCH, RS, LDPC와 같은 수많은 기법들이 연구되고 그 성능이 입증됐다. 하지만, ECC 기법은 성능이 좋아질수록 그 알고리즘의 복잡도가 상승하므로 현재까지 NAND flash memory에 적용된 ECC 기법은 BCH code가 대부분이었다. [13,14] 이는 BCH code가 error correction 성능 면에서는 조금 떨어지지만, 부호/복호화가 간단하여 하드웨어로의 구현이 쉽고 NAND flash memory로의 적용도 간편했기 때문이었다.

하지만, 보다 높은 error correction 성능을 확보하기 위해 LDPC와 같은 code의 채용이 부 분적으로 이루어지고 있다. 하지만 이 역시 NAND flash memory의 채널 모델에 대한 정의 가 선행되어야 할 것이며 성능 및 구현 면적에 미치는 영향이 적도록 하드웨어로 구현되어 NAND flash memory에 최적화된 알고리즘으 로 변형되는 것이 필수적이라고 생각된다.

#### 4. Flash Translation Layer

Flash Translation Layer (FTL)은 파일 시스템과 NAND flash memory 사이에서 NAND flash memory를 기존 블록 디바이스처럼 보이게 하여 기존 파일 시스템의 수정 없이 NAND flash memory를 저장장치로 사용할 수 있게 해주는 소프트웨어 layer이다.

NAND flash memory를 기존 OS와 맞물려 사용하는 방법에는 크게 FTL를 사용하는 방법 과 전용 file system을 만드는 방법이 존재한다. 두 쪽 모두 장단점이 존재하지만 본고에서는 보다 적은 memory를 사용하고 유지보수가 쉬우며 기존 파일 시스템과 함께 쉽게 사용할 수 있다는 장점이 있는 FTL에 집중하도록 한다.

FTL을 분류하는 가장 큰 기준은 논리적 주소를 물리적 주소로 변환해주는 단위이다. 먼저 논리주소를 NAND flash memory의 블록 단위로 주소를 변환하는 테이블을 가지는 FTL을 block mapped FTL 이라 하며, 페이지 단위로 주소를 변환하는 테이블을 가지는 FTL을 page—apped FTL 이라 한다. 또한, 이 두 가지 방식을 적절히 혼합하여 사용하는 형태의 FTL도 연구됐다. [15~17] 이러한 FTL들은 주소 변환 테이블의 크기가 크지만 효율적인 flash memory의 관리가 가능한 page—mapped FTL과 주소 변환테이블의 크기는 작지만 flash memory의 관리가 어려운 block—mapped FTL의 장점만을 효율적으로 결합한 기법들이다. 요약하면, 자주 접근되는 테이블을 flash memory보다 접근 속도

가 빠른 SRAM 또는 DRAM에 저장하기 위하여 그에 적당한 크기의 주소 변환 테이블을 만드는 것이 화두였던 것이다.

현재까지 연구되었던 FTL 들의 또 한 가지 주 요한 관심사는 위와 같은 적당한 크기의 주소 변환 테이블을 가지면서도 성능 저하를 최소화하는 효율적인 garbage collection 기법이다. 즉, 하나의 입출력 요청을 처리하기 위하여, 부가적으로 필요한 flash memory 연산의 개수를 줄이기 위한 노력이 지속되고 있다.

그렇다면 앞으로의 FTL은 어떻게 변해갈 것인가? 현재까지의 FTL의 관심사가 주소 변환 테이블의 크기와 효율적인 garbage collection에 비슷하게 나누어져 있어 block—mapped FTL과 page—mapped FTL의 혼합된 형태의 FTL이 주를 이루었다면, 이제는 보다 성능에 초점을 맞추어 page—mapped FTL 형태의 FTL의 주를 이룰 것으로 생각한다. 이는 지금까지의 FTL들이 다루고자 했던 가장 큰 목적 중의 하나인 작은 크기의 임의 접근의 성능을 높이기에 가장 탁월한 방법임이 분명하기 때문이다. 하지만, 여전히 주소 변환 테이블 저장 공간의 문제가 남아있어 주소 변환 방법의 계층구조를 두거나 필요한부분만 선택적으로 빠른 메모리로 로딩하는 등의 연구가 활발히 진행되고 있다. [17,18]

이와 더불어, NAND flash memory 셀들의 수명을 연장하는 wear-leveling 기법과 불량 셀들의 사용을 효율적으로 피하는 bad-block management 기법도 지속적으로 연구되고 있다.

앞으로의 FTL은 그 기능적 복잡도가 SSD 내부 프로세서의 계산 능력을 초과할 정도로 증가함에 따라, SSD 성능 저하의 주요인이 될 가능성이 있다. 따라서, FTL의 일부 기능을 하드웨어 가속기로 구현하는 추세가 증가할 것이다. 또

다른 대안은 다중 프로세서 구조의 SSD 제어기가 출현하여, 다수 개의 프로세서가 작업을 분담하는 형식으로 FTL 복잡도 증가에 대처하는 것이다.

#### 5. Software for SSD

SSD가 시장에서 자신의 위치를 굳건히 다져가면서 SSD 내부뿐 아니라 외부에서의 최적화 또한 함께 이루어지고 있다. 이 중 최근 가장 눈에 띄는 것 중 한 가지는 Microsoft Windows 7의 trim 명령어 지원이다. [19] 이에 따르면 SSD는 ATA8-ACS identify word 217을 통해 HDD와 자신을 구분 지을 수 있으므로 Windows가 장착된 SSD를 인식하여 wear-leveling 및 성능향상을 위한 여러 작업을 사전에 할 수 있다는 것이다. 이를 완벽히 지원하기 위해서는 SSD에서도 어느 수준 이상의 읽기 반응 시간을 보장해야 하는 등의 여러 제약사항이 따르지만 실제로 적용될 경우 SSD의 수명 및 성능 측면에서 큰 효과를 볼 수 있을 것이라 기대된다.

### V. 결 론

지금까지 NAND flash memory와 그 다양한 응용 분야들, 그리고 그 중 가장 주목을 받는 SSD에 대해 알아보았다. NAND flash memory 는 현재 가장 큰 시장을 가지는 메모리로서 여러 응용 분야에서 활용되고 있다. 하지만, SSD의 경우에는 HDD를 대체할 저장장치로 주목을 받고는 있지만 아직 시장에서의 높은 가격과 몇몇 기술적 문제로 아직은 시장을 주도하지 못하는 것이 현실이다. 하지만, SSD 관련 기술들이 전

세계적으로 큰 관심 속에서 연구되고 있기 때문에 곧 현재수준보다 훨씬 저렴한 가격, 그리고 뛰어난 성능의 SSD가 개발되어, HDD 위주의 대용량 저장시장에 변혁을 가져오리라 예측된다.

### === 참고문헌 =

- [1] Grand Eskelsen, Adam Marcus, W. Kenneth Ferree, "The Digital Economy Fact Book. Tenth Edition," The Progress & Freedom Foundation, 2009.

- [2] Ken Takeuchi, "Novel Co-Design of NAND Flash Memory and NAND Flash Controller Circuits for Sub-30 nm Low-Power High-Speed Solid-State Drives (SSD)," IEEE Journal of Solid-State Circuits, Vol.44, No.4, April, 2009.

- [3] David Reinsel and Jeff Janukowicz, "White Paper: Datacenter SSDs: Solid Footing for Growth, "http://www. samsung.com/global/business/semicon ductor/products/flash/ssd/2008/down /datacenter\_ssds.pdf, January, 2008.

- [4] "Samsung NAND Flash Memory," Samsung Memory Product & Techonology Division, March, 2000.

- [5] Raz Dan and Rochelle Singer, "White Paper: Implementing MLC NAND Flash for Cost-Effective, High-Capacity Memory," http://www.data-io.com/pdf/NAND/MSystems/Implementing \_MLC\_NAND\_Flash.pdf, September, 2003.

- [6] ONFI, http://onfi.org/.

- [7] Dushyanth Narayanan, Eno Thereska, Austin Donnelly, Sameh Elnikety, Antony Rowstron, "Migrating Server Storage to SSDs: Analysis of Tradeoffs," EuroSys'09, Nuremberg, Germany, April, 2009.

- [8] Sang-Won Lee, Bongki Moon, Chanik Park, Jae-Myung Kim, Sang-Woo Kim, "A Case for Flash Memory SSD in Enterprise Database Applications," SIGMOD '08, Vancouver, BC, Canada, June, 2008.

- [9] Seon-yeong Park, Dawoon Jung, Jeong -uk Kang, Jin-soo Kim, and Joonwon Lee, "CFLRU: A Replacement Algorithm for Flash Memory," CASES'06, Seoul, Korea, October, 2006.

- [10] Hyojun Kim and Seongjun Ahn, "BPLRU: A Buffer Management Scheme for Improving Random Writes in Flash Storage," FAST '08: 6th USENIX Conference on File and Storage Technologies, 2008.

- [11] Jin Kyu Kim, Hyung Gyu Lee, Shinho Choi, Kyoung Il Bahng, "A PRAM and NAND Flash Hybrid Architecture for High-Performance Embedded Storage Subsystems," EMSOFT"'08, Atlanta, Georgia, USA, October, 2008.

- [12] Neal Mielke, Todd Marquart, Ning Wu, Jeff Kessenich, Hanmant Belgal, Eric Schares, Falgun Trivedi, Evan Goodness, and Leland R. Nevill, "Bit

- Error Rate in NAND Flash Memories," IEEE CFP08RPS-CDR 46th Annual International Reliability Physics Symposium, Phoenix, 2008.

- [13] Wei Liu, Junrye Rho, Wonyong Sung, "Low-Power High-Throughput BCH Error Correction VLSI Design for Multi-Level Cell NAND Flash Memories," Signal Processing Systems Design and Implementation, 2006, SIPS '06, IEEE Workshop on, October, 2006.

- [14] Fei Sun, Ken Rose, and Tong Zhang, "On the Use of Strong BCH Codes for Improving Multilevel NAND Flash Memory Storage Capacity," Signal Processing Systems Design and Implementation, 2006, SIPS '06, IEEE Workshop on., Oct., 2006.

- [15] J. Kim, J.M. Kim, S.H. Noh, S.L. Min, and Y. Cho, "A space-efficient flash translation layer for CompactFlash systems," Consumer Electronics, IEEE Transactions on, Vol.48, No.2, pp.366-375, May, 2002.

- [16] S.W. Lee, W.K. Choi, and D.J. Park, "FAST: An efficient flash translation layer for flash memory," EUC Workshops 2006, pp.879-887, 2006.

- [17] J.U. Kang, H. Jo, J.S.Kim, J. Lee, "A superblock-based flash translation layer for NAND flash memory," EMSOFT'06, Oct., 2006.

- [18] Aayush Gupta, Youngjae Kim, Bhuvan

- Urgaonkar, "DFTL: A Flash Translation Layer Employing Demand-baed Selective Caching of Page-level Address Mappings," ASPLOS '09, Washington, DC, USA, March, 2009.

- [19] Frank Shu, "Windows 7 Enhancements for Solid-State Drives," Microsoft WinHEC 2008, 2008.

#### 저자소개

방 관 후

2006년 연세대학교 기계전자공학부 학사 2008년 연세대학교 전기전자공학과 석사 2008년~현재 연세대학교 전기전자공학과 박사과정

주관심 분야: 저전력 설계 기술, 플래시 메모리 응용, 바 이오 응용

### 저자소개

박 상 훈

2009년 연세대학교 전기전자공학과 학사 2009년~현재 연세대학교 전기전자공학부 석사과정

주관심 분야 : 시스템 구조, 플래시 메모리 응용

정 의 영

1988년 고려대학교 전자전산공학과 학사 1990년 고려대학교 전자공학과 석사 2002년 스탠포드 대학교 electrical engineering 박사 1990년~2005년 삼성전자 SoC 연구소 수석 연구원 2005년~현재 연세대학교 전기전자공학부 부교수

주관심 분야: 시스템 구조, 저전력 설계 기술, 플래시 메 모리 응용, 바이오 응용